时序逻辑

1.锁存器与触发器

时序逻辑电路特点

- 当时的输出由当时的输入与电路的当前(原来)状态决定——具有“记忆”功能

- 对于触发器有两个互非的输出Q,$\overline{\text{Q}}$,Q=0时为0态,Q=1时为1态

- 无外加信号作用时,触发器保持原态→n级触发器可以记忆n位二进制信息的2n种状态

- 在外加信号的作用下,触发器可以改变原态(置1和置0)

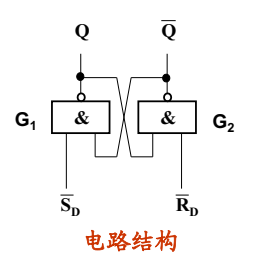

基本RS锁存器

- 保持功能:触发器保持原来的状态不变→$\overline{\text{R}}$=1,$\overline{\text{S}}$=1

- 置0功能:$\overline{\text{R}}$=0,$\overline{\text{S}}$=1

- 置1功能:$\overline{\text{R}}$=1,$\overline{\text{S}}$=0

- 约束条件:$\overline{\text{R}}$+$\overline{\text{S}}$=1(R与S不同时为1)

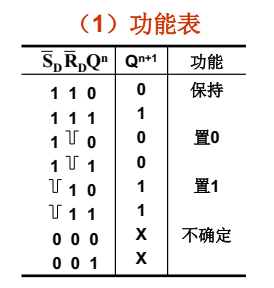

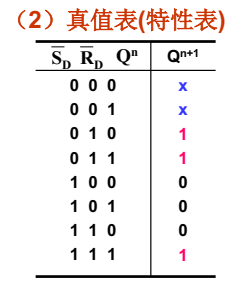

- 功能表:

- 真值表:

- 特性方程:Qn+1=S+$\overline{\text{R}}$Qn

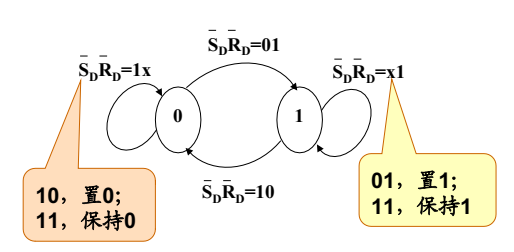

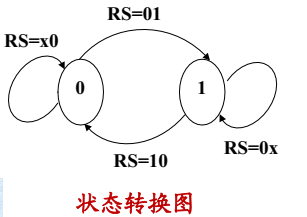

- 状态转换图:

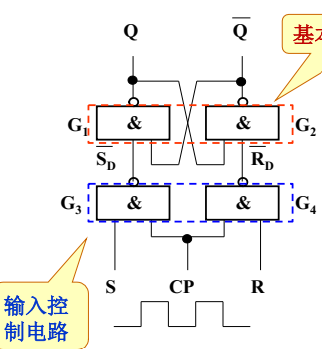

钟控RS锁存器

- 电位触发:在控制电位CP的控制下接收数据(正负电位触发均有可能)

- CP=0时,无论R与S的输入如何,均保持原有状态

- CP=1时,同基本锁存器(由R与S决定)

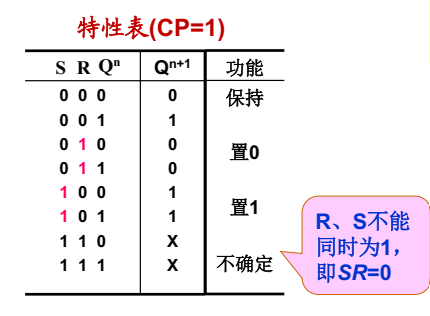

- 特性表:

- 特性方程:Qn+1=S+$\overline{\text{R}}$Qn

- 状态图:

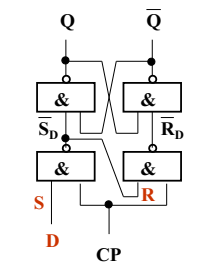

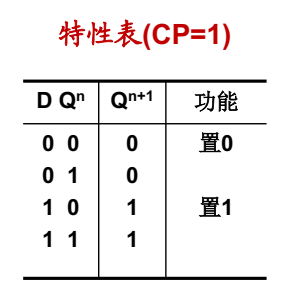

钟控D锁存器

- 改进之处:将钟控RS锁存器的输入由R、 S双端输入改为单端输入(D)→S,R总是互非,钟控D锁存器不会出现不定状态(消除不确定状态)

- CP=0时同上

- CP=1时,状态由D输入决定

- 特性表:

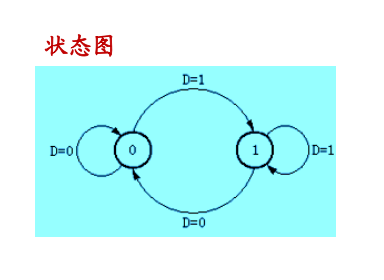

- 特性方程:Qn+1=D

- 状态图:

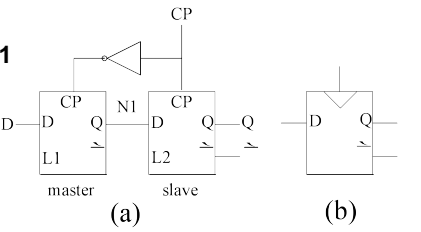

D触发器

- 锁存器与触发器的区别:锁存器是电位触发→只有CP处于有效电位时,状态才有可能发生发生变化;触发器的状态变化只发生在CP的有效沿(上升、下降都可能),CP=1/0时不会发生变化

- 构成:由两个相反(CP相反)的D钟控锁存器组成,L1为主锁存器,L2为从锁存器

- CP=0时,L1通,Q1←D;L2断,Q2不变

- CP:0→1时,L1断,Q1不变;L2通,Q2←Q1(触发时刻)

- CP=1时,L1断,Q1不变;L2通,Q2与Q1一样也不变

- 使能信号:EN=1时,D触发器正常工作;EN=0时,D触发器状态不变

- 复位信号:RESET=1时,D触发器复位(Q=0);RESET=0时,D触发器正常工作

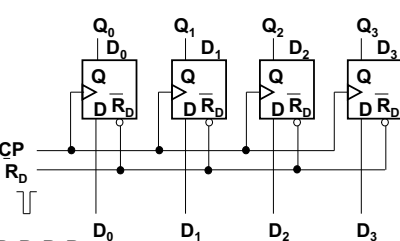

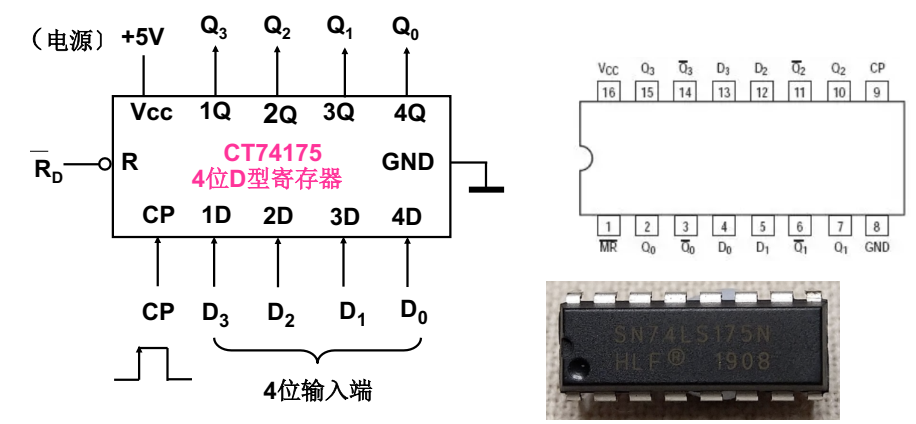

- 寄存器:

(1)$\overline{\text{R}}$=0时,Q0Q1Q2Q3=0000

(2)CP上升沿来到时,Q0Q1Q2Q3=D0D1D2D3

工作方式:并入并出

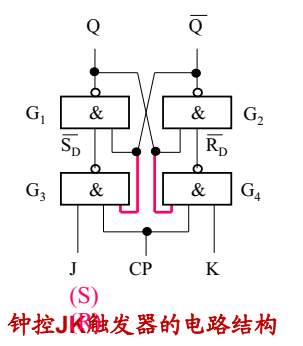

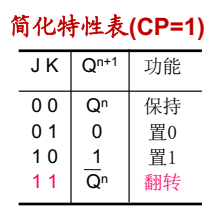

JK锁存器

- JK锁存器与D触发器的区别:后者无法做到保持原态(CP=1时);前者增加两条反馈线,把R改为K,S改名为J→没有约束条件,把RS= 11的无效状态变为JK触发器的翻转(计数) 功能

- CP=0时,保持原态

- CP=1时,由J、K决定状态

- 特性表:

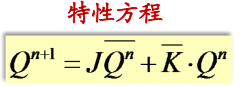

- 特性方程:

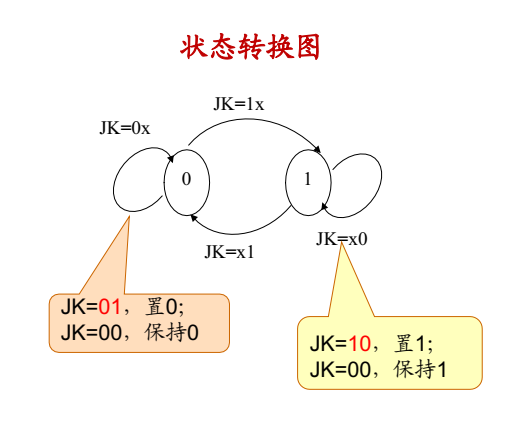

- 状态图:

2.有限状态机

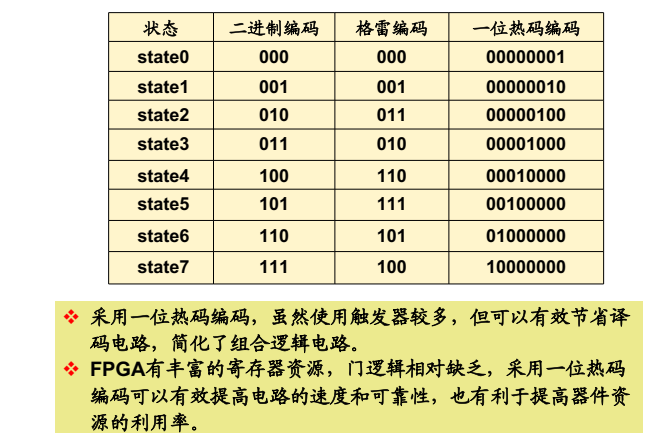

状态编码方式

- 二进制编码:采用log2N个触发器来表达N个状态→可能产生毛刺

- 格雷编码:触发器数量同上,但编码方式不同:G(x)=x⊕(x/2)

- 独热码编码:采用N个触发器来表达N个状态

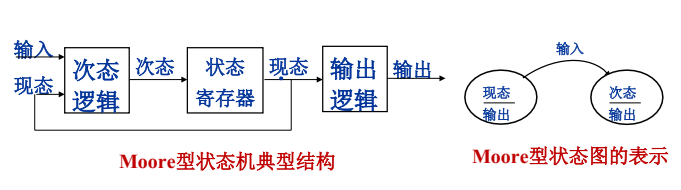

Moore型有限状态机

- 输出只与当前状态有关,与外部输入无关

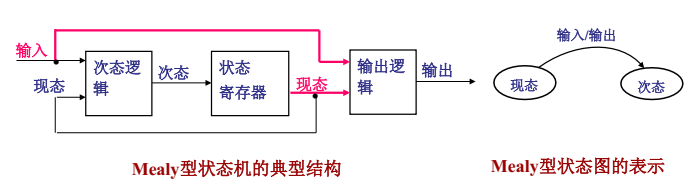

Mealy型有限状态机

- 输出与当前状态和外部输入均有关

有限状态机设计步骤

- 分析设计要求,列出全部的可能状态

- 根据上述的状态逐个对其进行分析,画出状态图

- 根据状态图列出状态转换表

- 根据状态转换表写出次态逻辑表达式和输出逻辑表达式

- 根据逻辑表达式写出逻辑图

3.时序逻辑电路设计分析

数据寄存器

- 四位二进制数寄存器CT74175

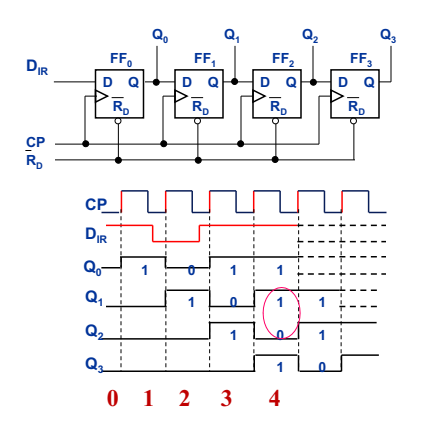

移位寄存器(移存器)

- 描述:具有移位功能的寄存器→每来一个时钟脉冲,寄存器中的数据就向左或向右移动一位

四位右移移位寄存器

- 串入并出:经过4个周期,串行输入的4个数据全部进入寄存器,通过Q0~Q3并行输出→实现串并转换

- 串入串出:把最右边的触发器的输出作为电路的输出。经过4个周期后,Q3开始输出4个数据→实现延迟输出

此种工作方式下,每个触发器的输出波形相同,但是后级触发器的输出比其前级输出慢一个周期

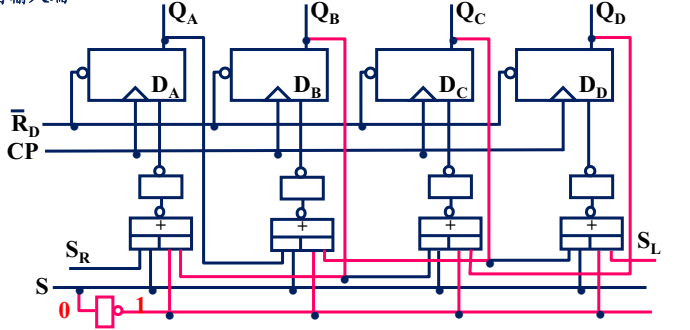

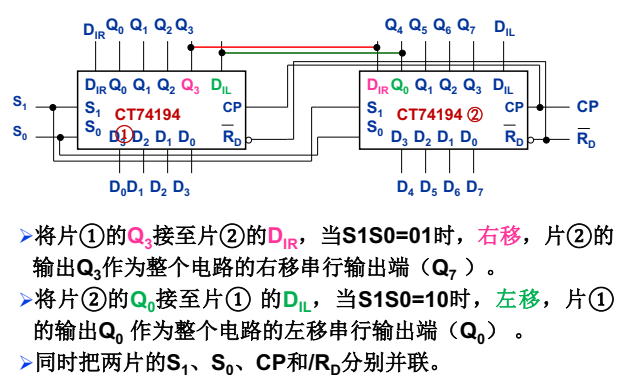

四位串行输入双向移位寄存器

- 工作原理:S=0(1),往左(右)移;SR:右移串行输入端;SL:左移串行输入端

- S=1时,为右移移位寄存器:功能同上

- S=0时,为左移移位寄存器,功能同上,方向相反

串入并出→串转并输出

串入串出→延迟输出

并入串出→并转串输出

并入并出→数据预置移位寄存器的拓展

计数器

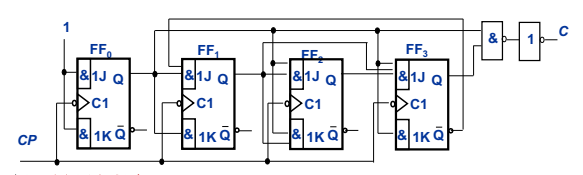

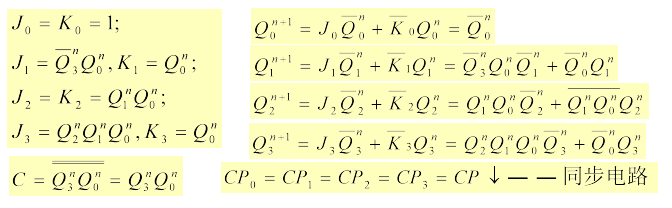

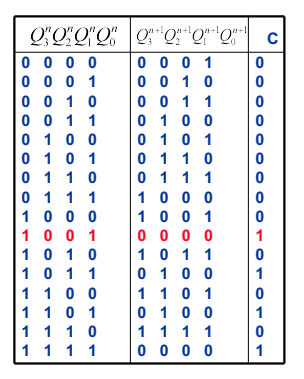

同步计数器

计数器有许多不同的分类方式:

- 电路结构:

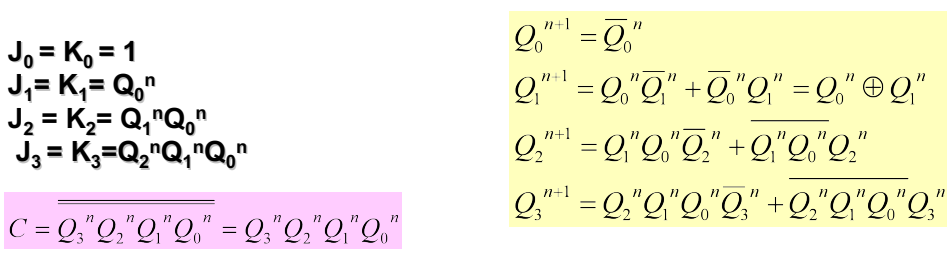

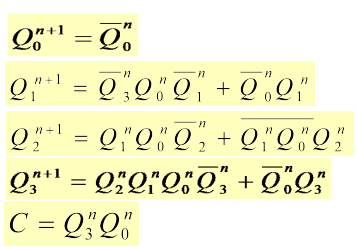

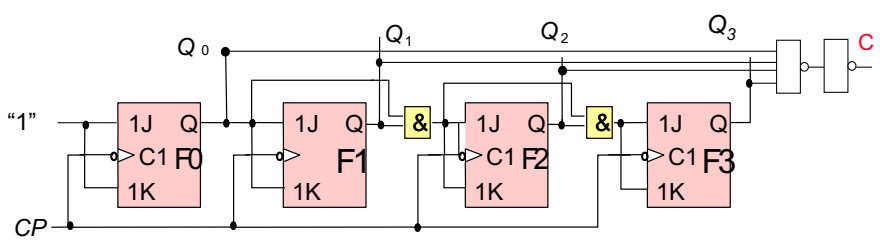

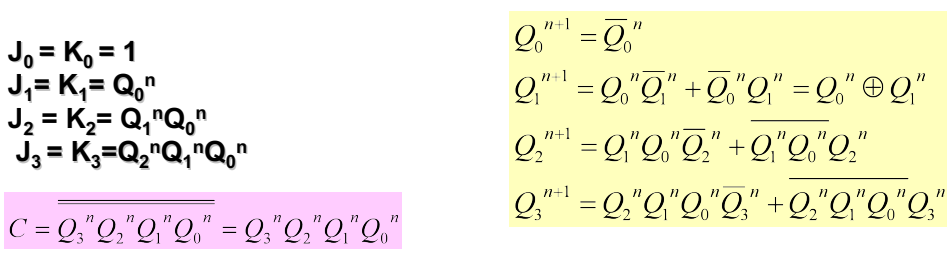

- 方程式:

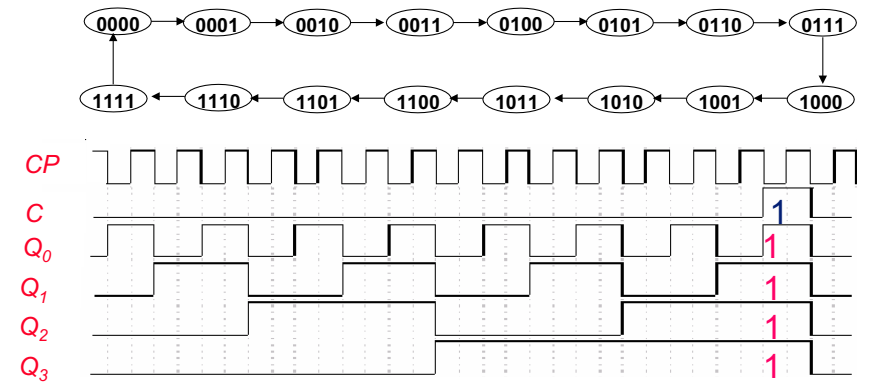

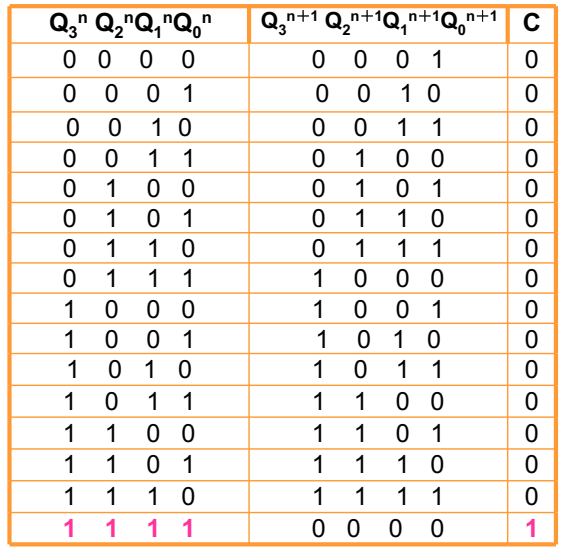

- 状态转换表

- 逻辑表达式

- 电路结构:

- 方程式:

- 状态转换表

- 逻辑表达式